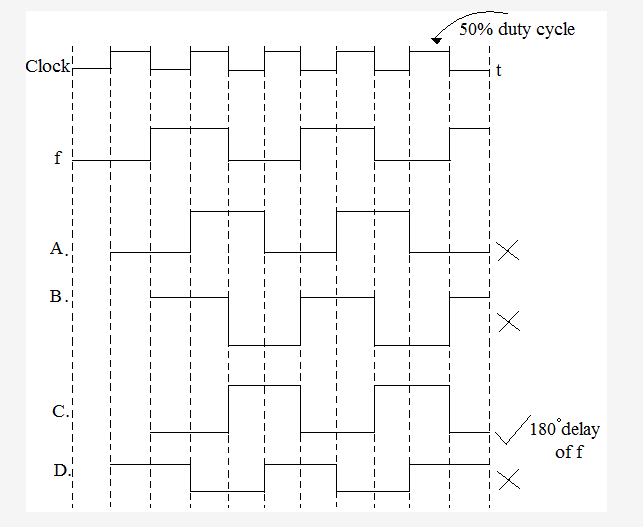

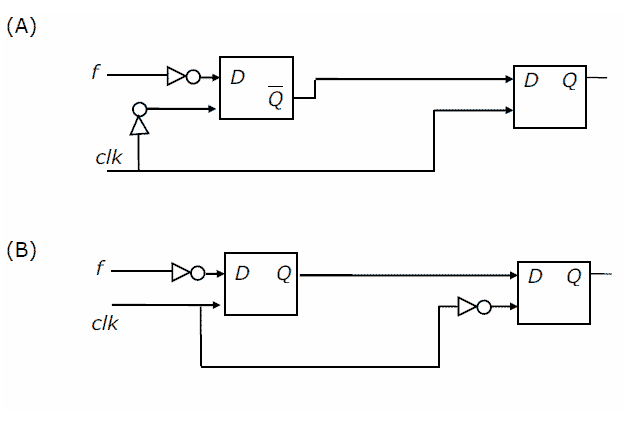

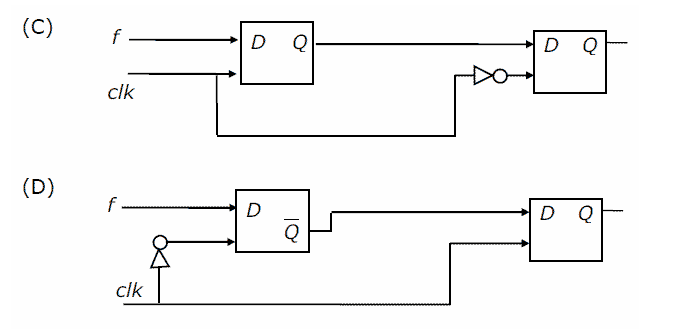

Q. 40 You are given a free running clock with a duty cycle of 50% and a digital waveform f which changes only at the negative edge of the clock. Which one of the following circuits (using clocked D flip flops) will delay the phase of f by 180c ?

Explanation: