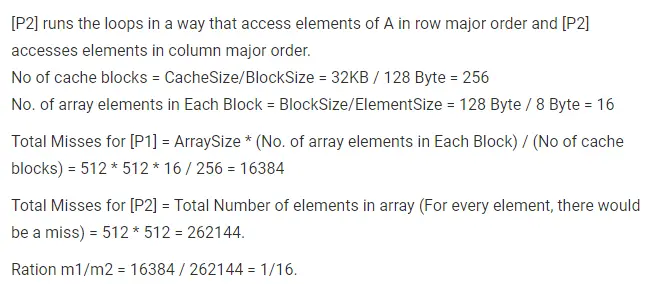

Q. 33 A CPU has a 32 KB direct mapped cache with 128-byte block size. Suppose A is a two dimensional array of size 512 X 512 with elements that occupy 8-bytes each. Consider the following two C code segments, P1 and P2, P1 :

P1:

for (i=; i<512; i++) { for (j=; j<512; j++) { x +=A[i] [j]; } }

P2:

for (i=; i<512; i++) { for (j=; j<512; j++) { x +=A[j] [i]; } }

P1 and P2are executed independently with the same initial state, namely, the array A is not in the cache and i, j,x are in registers. Let the number of cache misses experienced by P1 be M1 and that for P2 be M2. The value of M1 is

(A) 0

(B) 1/16

(C) 1/8

(D) 16

Answer: (B)

Explanation: