Q. 65 Consider a three word machine instruction

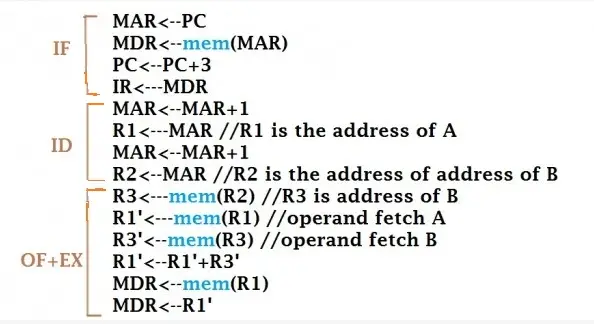

ADD A[R0], @ B

The first operand (destination) “A [R0]” uses indexed addressing mode with R0 as the index register. The second operand (source) “@ B” uses indirect addressing mode. A and B are memory addresses residing at the second and the third words, respectively. The first word of the instruction specifies the opcode, the index register designation and the source and destination addressing modes. During execution of ADD instruction, the two operands are added and stored in the destination (first operand).

The number of memory cycles needed during the execution cycle of the instruction is

(A) 3

(B) 4

(C) 5

(D) 6

Answer: (B)

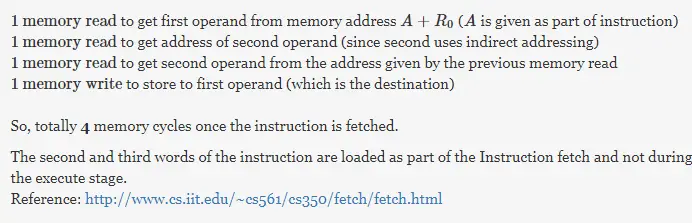

Explanation: