Q. 67 A processor uses 2-level page table fro virtual to physical address translation.

Page table for both levels are stored in the main memory. Virtual and physical

addresses are both 32 bits wide. The memory is byte addressable. For virtual to

physical address translation, the 10 most significant bits of the virtual address are

used as index into the first level page table while the next 10 bits are used as

index into the second level page table. The 12 least significant bits of the virtual

address are used as offset within the page. Assume that the page table entries in

both levels of page tables are 4 a bytes wide. Further, the processor has a

translation look aside buffer(TLB), with a hit rate of 96%. The TLB caches

recently used virtual page numbers and the corresponding physical page numbers.

The processor also has a physically addressed cache with a bit ratio of 90%. Main

memory access time is 10 ns, cache access time is 1 ns, and {LB access time is

also 1ns.

Assuming that no page faults occur, the average time taken to access a virtual

address is approximately (to the nearest 0.5 ns)

(A) 1.5 ns

(B) 2 ns

(C) 3 ns

(D) 4 ns

Answer: (D)

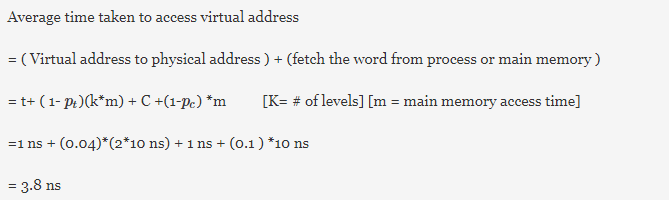

Explanation: